�Ї����w�W(w��ng)Ӎ �ڰ댧(d��o)�w�a(ch��n)�I(y��)�İl(f��)չ�v���У�Ħ�������L�����I(l��ng)��оƬ���ܵ������cҎ(gu��)ģ�ĔU����Ȼ��,���S�����w�ܳߴ粻��ƽ�����O��,����������Ч��(y��ng)�Ȇ��}�����@�����y(t��ng)���g(sh��)·������ƿ�i,������ͨ�ף�TGV�����g(sh��)�{�誚��(y��u)��,����ɞ�댧(d��o)�wͻ��Ħ���������`,���_�������L�������P(gu��n)�I������

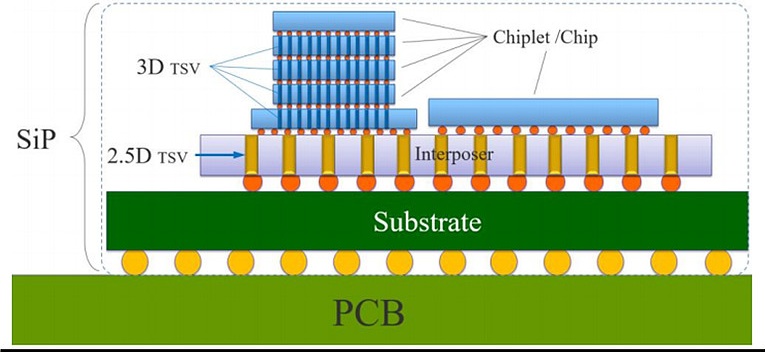

2.5D/3D���b��ˇ�е�TSV���g(sh��)

�҂���֪��,��Ҫ���F(xi��n)оƬ���ܵ���������Ҫ�ѯB����ľ��w�ܣ�����(j��)��Ħ�����ɡ�,��оƬ���ݼ{�ľ��w�ܔ�(sh��)Ŀÿ18��24��������һ��,���^ȥ��(sh��)ʮ�꣬���S��Ħ�����ɡ����M(j��n),����λ��e���w���ܶȳ��m(x��)����,���(q��)��оƬ�������ͻ����M(j��n)�������������֙C,���Pӛ����X��һϵ�б�yʽ��Ӯa(ch��n)Ʒ,����������˴������c���M�ΑB(t��i),��

����Ħ�����ɡ��K���|���컨���һ��,����(d��ng)���A���칤ˇ���M(j��n)��14nm,��7nm��5nm,��ֱ����(d��ng)����ǰ�ص�3nm,������Ч�����l(f��)�ܵ���(y��n)������(zh��n)����ˇ���M(j��n)�e���S�D,��������������ƿ�i���ɱ��s��Ó�\Ұ�R�����j��,��

���������AI�˳�ϯ��ȫ��,��AI����(w��)��������������ʾ���ʽ���l(f��),�����������ı����Ȼ��Ҫ����оƬ֧��,��������оƬ�����Ƿ�ֻ����ه��̹�ˇ�ij��m(x��)ͻ�ƣ����Ƿ�,����(d��ng)ǰоƬ�Ѹ߶��ͻ�,���ҷ���(w��)�����p������Ҫ���h(yu��n)�������M��ӣ�һ�lȫ��˼·��(y��ng)�\��������ͨ�^�ѯB���wоƬ���F(xi��n)�����S��,�����Ǻ�����ı�������һ��(ji��)��܇�^�������ǾͶ�Ӄɹ�(ji��),���q��ղ���Ӯ�(d��ng)��Ľ�Q˼·��

�ɴˮa(ch��n)���ˆ��},��оƬ�ѯB��Ό��F(xi��n),��

Ŀǰ���M(j��n)���b�֞�ɴ��һ������XYƽ����������M(j��n)���b���g(sh��),����Ҫͨ�^�ز����ӹ�ˇ��RDL���M(j��n)����̖������ͻ��B����,������Z�S��������M(j��n)���b���g(sh��),����Ҫ��ͨ�^��ͨ�ף�TSV���M(j��n)����̖����ͻ��B,���@Ȼ,��оƬ�ѯB���ڵڶ��N��ͨ�^TSV���g(sh��),�����Ԍ�����оƬ�M(j��n)�д�ֱ�ѯB�����B,�����ռ�����͵IJ�ͬ�֞�2.5D TSV��3D TSV��2.5D TSVָ����λ�ڹ��D(zhu��n)�Ӱ��ϵ�TSV,��3D TSV��ָ؞��оƬ�w֮��,���B������оƬ��TSV����3D TSV��,��оƬ�����,���������t�����٣��һ��B�L�ȿs��,���ܜp�����P(gu��n)����Ч��(y��ng),��ʹ�����Ը��ߵ��l���\�У��Ķ��D(zhu��n)�������ܸ��M(j��n),��������̶ȵĽ��ͳɱ�,��TSV�ijߴ緶�����^��ij��^100um,��С��С��1um,���S����ˇˮƽ������TSV����Խ��ԽС,���ܶ�Խ��Խ��,��

����TSV���g(sh��)��ϵ�y(t��ng)�����b ��Դ:�f(li��n)�Cȯ�о���

TGV��TSV������

�mȻ�����M(j��n)���b�I(l��ng)��TSV���g(sh��)�^�����,��������ڃɂ���Ҫ���}��

�ɱ��ߣ�����������ȹ辧�A������^��,������������,���p�Ĵ�ˇ��(f��)�s,��������g,���������Ⱦ���(x��)�h(hu��n)��(ji��)���O(sh��)�侫��Ҫ���,����ُ���S�o(h��)�ɱ��@��,�����ʵͣ�ȱ�݆��}��(d��o)�³ɱ�����,��

늌W(xu��)���ܲ����ό��ڰ댧(d��o)�w����,����ݔ���ڂ�ݔ��̖�r����̖�c�r�ײ������^����늴����Ч��(y��ng),���r���Юa(ch��n)���u���F(xi��n)��,�������̖�������^���p����?d��ng)_�ȣ�,��

���^����D(zhu��n)�Ӱ�,�������D(zhu��n)�Ӱ����T����(y��u)�ݣ�

һ���ͳɱ��������ڴ�ߴ糬����岣�����ګ@ȡ,���Լ�����Ҫ���e�^����,���ɱ���ͣ�

��,����(y��u)���ĸ��l늌W(xu��)���ԣ�����������һ�N�^���w����,����늳���(sh��)ֻ�й���ϵ�1/3���ң��p�����ӱȹ���ϵ�2~3����(sh��)����,��ʹ���r�דp�ĺͼ���Ч��(y��ng)���pС,��������Ч��߂�ݔ��̖�������ԣ�

��,����ߴ糬�������r�����ګ@�,����������������Լ�Ф�صȲ����S�̿������a(ch��n)����ߴ磨����2m��2m���ͳ��,���С��50��m������岣���Լ��������Բ�������,��

�ġ���ˇ���̺��Σ�����Ҫ���r�ױ��漰TGV��(n��i)�ڳ��e�^����,���ҳ����D(zhu��n)�Ӱ岻��Ҫ���Μp�,���

��,���Cе��(w��n)���ԏ�����(d��ng)�D(zhu��n)�Ӱ���С��100��m�r,���N����Ȼ�^С��

TGV���g(sh��)�h(yu��n)�ڳ��L���g�V�

Ӣ���_(d��)��H100����Ӌ�㿨�����_�e�CoWoS-S 2.5D���b���g(sh��),���ڹ��D(zhu��n)�Ӱ��ό��F(xi��n)7�MоƬ���B,��AMD�������댧(d��o)�w��MI300��ȡ��Ʋ��֣���CoWoS��ˇ�ڹ��D(zhu��n)�Ӱ��Ϸ��b6�wGPU,��3�wCPU��8�MHBM��(n��i)��,������(n��i)���棬����Ƽ�BR100ϵ��GPUҲ����CoWoS-S���b,����2�wӋ��о�,����B�����F(xi��n)�����Ŀ�Խʽ����,��

CoWoS���b�ĺ���֮һ����D(zhu��n)�Ӱ弰TSV��ˇ,��������ڳɱ��ߺ�늌W(xu��)���ܲ�Ȳ��㣬�������D(zhu��n)�Ӱ弰TGV��ˇ���еͳɱ�,���@ȡ,�����l늌W(xu��)���ԃ�(y��u)�������ԣ����,��TGV��������ǰ�����Ʒ,���ɞ����M(j��n)���b�������M(j��n)����֮һ���B��AI�˳�֮�¼���Ӌ��оƬ�������,��TGV�h(yu��n)�ڳ��L���g�V�,���䌍����ֹ�������D(zhu��n)�Ӱ�,������TGV���g(sh��),�����������ڹ��ϵ�y(t��ng)�����I(l��ng)��MEMS���b���I(l��ng)��Ҳ�о�đ�(y��ng)��ǰ��,����������IC�d��ʹ��,�����ڲ����I(l��ng)������F(xi��n)���������ЙC�d�塣

������Դ:

���.оƬ���S���B���g(sh��)�����|(zh��)�����о��M(j��n)չ

ꐿ���.������5GͨӍ�еđ�(y��ng)��

�|���Cȯ�����M(j��n)���b���m(x��)���M(j��n),������������пɞ顷

(�Ї����w�W(w��ng)������/����)

ע:�DƬ���̘I(y��)��;,�������֙�(qu��n)��֪�h��!