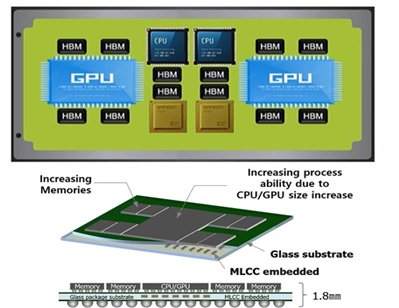

該中心將推進(jìn)32nm及22nm工藝半導(dǎo)體元件的微細(xì)化和高性能化。為此,將從高性能元件的試制及其電特性測試、納米級別的物理測量評價(jià)分析、第一原理電子狀態(tài)計(jì)算,、元件模擬等全方位的科學(xué)計(jì)算分析。

此外,,還將開發(fā)取代CMOS晶體管微細(xì)化的,、基于新原理的技術(shù),。這是因?yàn)椋?2nm工藝以后的微細(xì)化需要導(dǎo)入新材料、新構(gòu)造及新生產(chǎn)工藝,,但該領(lǐng)域預(yù)計(jì)到2020年左右將達(dá)到極限,。通過開發(fā)基于新原理的技術(shù),有望解決這一問題,。將建立與外部機(jī)構(gòu)共用的研發(fā)設(shè)施“NeIP(納米電子技術(shù)創(chuàng)新平臺)”,,與產(chǎn)綜研的其他部門及外部機(jī)構(gòu)合作,將其用作把基本技術(shù)與元件實(shí)證相結(jié)合的設(shè)施,。將以CMOS技術(shù)為基礎(chǔ),,高效試制新材料及新構(gòu)造元件,推進(jìn)可將測定數(shù)據(jù)和模擬試驗(yàn)結(jié)果進(jìn)行系統(tǒng)性積累的知識管理,。

另外,,該中心為了推進(jìn)新一代半導(dǎo)體的研發(fā),將繼續(xù)推進(jìn)通過NEDO(新能源產(chǎn)業(yè)技術(shù)綜合開發(fā)機(jī)構(gòu))委托的國家項(xiàng)目“半導(dǎo)體MIRAI項(xiàng)目”培育的技術(shù),。產(chǎn)綜研的新一代半導(dǎo)體研究中心等參與了半導(dǎo)體MIRAI項(xiàng)目,。產(chǎn)綜研稱,半導(dǎo)體MIRAI項(xiàng)目在應(yīng)變硅技術(shù)及高介電常數(shù)柵極絕緣膜技術(shù)等領(lǐng)域,,在保持 CMOS晶體管構(gòu)造的前提下提高性能方面取得了巨大成果,。但是,隨著CMOS晶體管的尺寸逐漸接近10nm原子水平,,需要開展包括半導(dǎo)體之外的技術(shù)領(lǐng)域在內(nèi)的研發(fā)等,,因此產(chǎn)綜研決定設(shè)立納米電子元件研究中心。